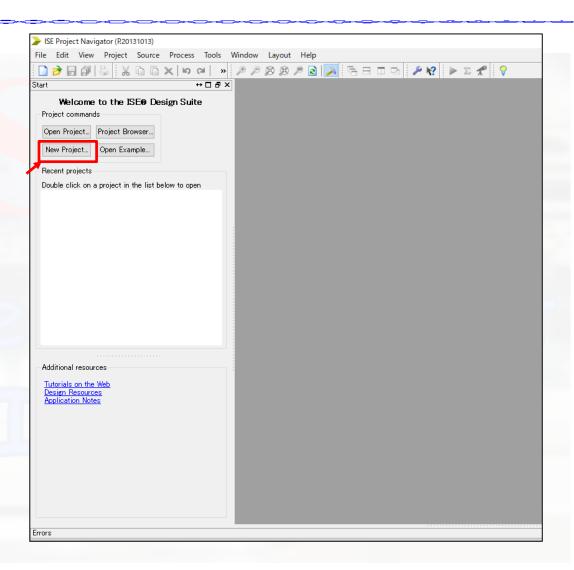

## Opening ISE Design Suite

- Open ISE Design Suite

- Note that the version used here is 14.7

■ Next, click the 「New Project...」 as shown in the figure.

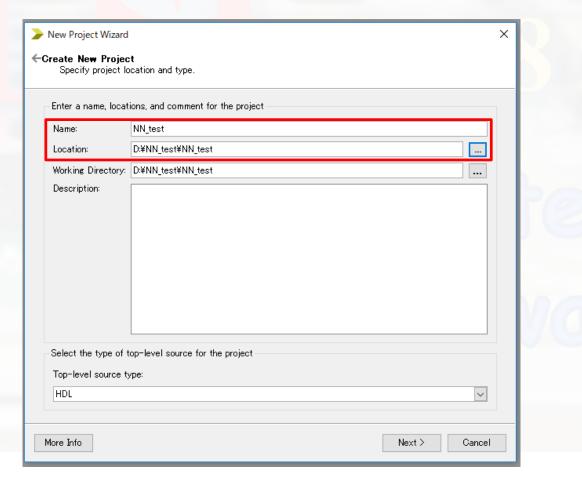

# Locating project file

- Assign the location to your selected folder

- Enter the name

- ■For example : NN\_test

- Click, next, next and finish.

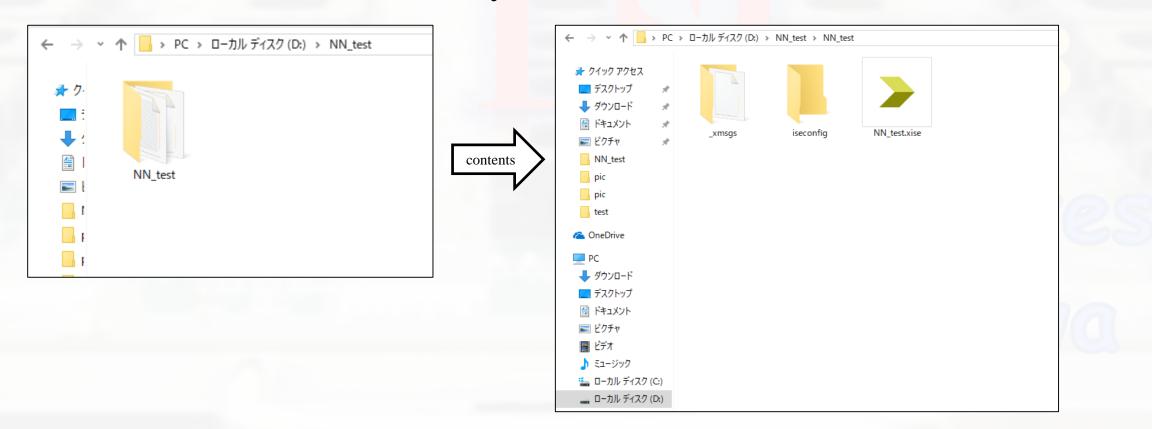

# Locating project file

A new folder will be created in your selected location

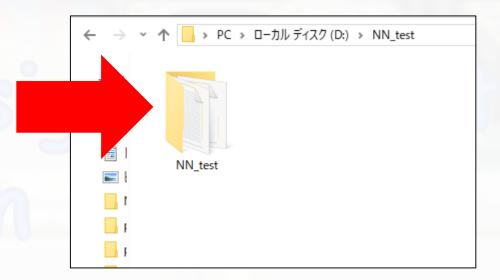

## Download Verilog file

- Download the zip file from LSI design contest HP.

- □Link: <a href="http://www.lsi-contest.com/shiyou\_4e.html">http://www.lsi-contest.com/shiyou\_4e.html</a>

- (Verilog file for simulation)

- Extract the file

- ☐ There will be around 45 Verilog file

- Move all the Verilog file into NN\_test folder

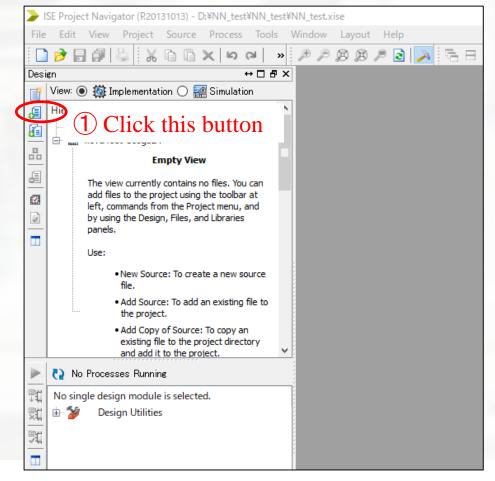

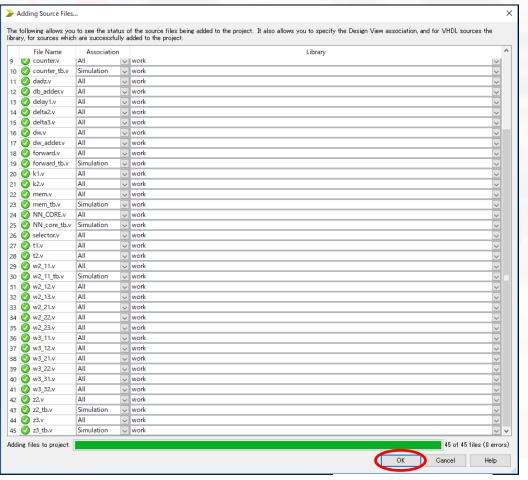

#### Add source file

Click Add source and select all the Verilog file

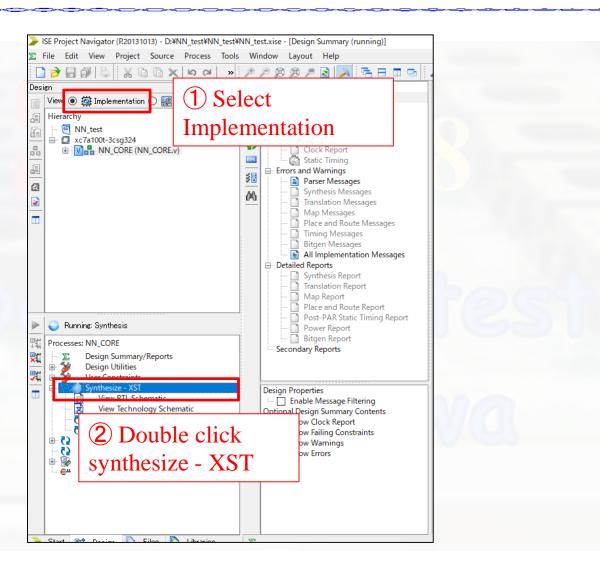

# Synthesize the project

- Select Implementation

- Double click synthesize XST

- Wait until it finish

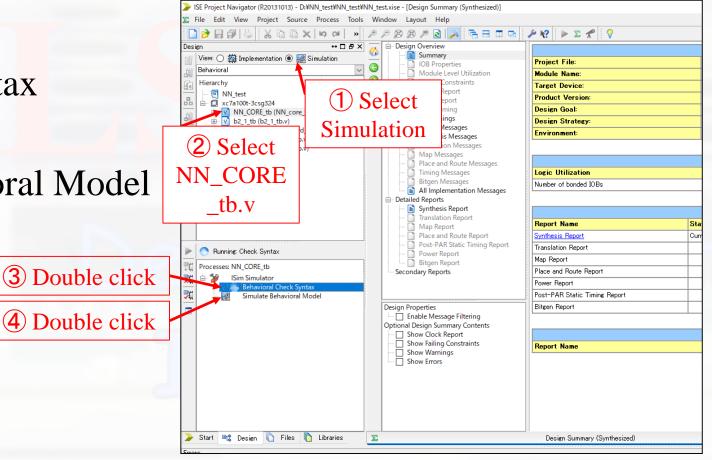

## Simulate the project

- Select Simulation

- Double Behavioral Check Syntax

- Wait until it finish

- Double click Simulate Behavioral Model

- ISE simulator will open

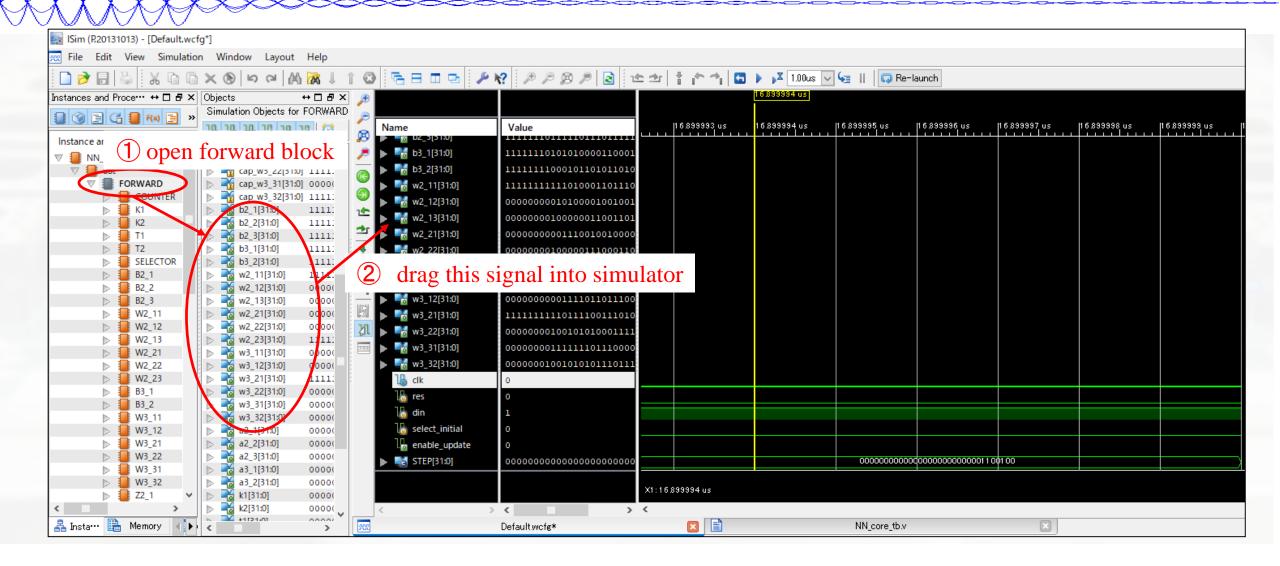

- Choose forward block in instance and process name

- □Choose signal b2\_1 until w3\_32

- □ Drag the signal into simulator

- Choose forward > selector block in instance and process name

- ☐ Choose signal enable update

- □ Drag the signal into simulator

- See the figure in the next slide...

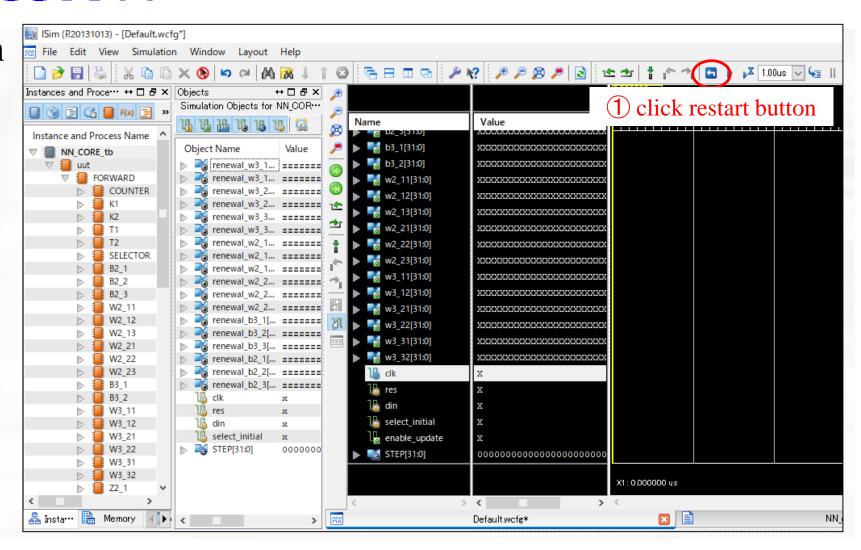

Click the restart button

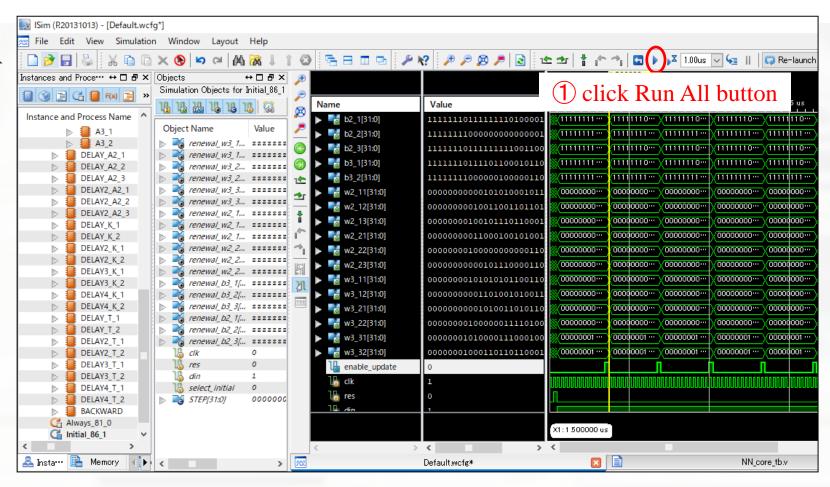

Click the Run All button

### Conclusion

- New weight and bias will be updated every time the enable update signal is active.

- In the current stage, the output does not converge.